ok, this afternoon , I tested the Quad , here is what i found.

- what is the bandwidth of the analog input channel?

From the connector to U5_pin13 and U16 _pin13 ,it is 10M .

lots of reasons for this .for example, the parasitic capacity around the U5 and U16, it is very distinct. - what is the sample rate ?

The max sample rate is 72M/s when T/div is 0.1us. Although we are seeking to make the sample rate to 144M when the other channel is unenabled, but now ,it seems not work .

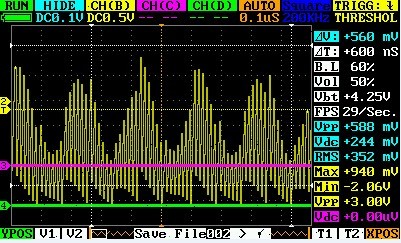

as in this picture , the signal is 5M. and you can see about 14 points in a period. so the sample rate is 72M ,and if the CHA was hiden, this wave mess up.

/.

as the 10M signal , the gain becomes about -6db. so , i believe we can say the bandwidth is 5M now