I have done some other test.

I am sorry but I can’t made any picture, so you should believe what I write…

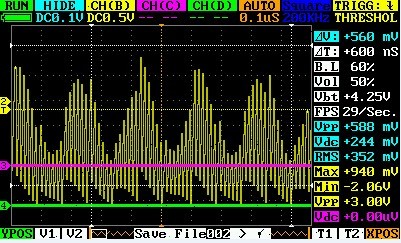

Generator: HP33120A

Reference scope: LeCroy LC358 1GHz

I have placed a 50 Ohms load on the generator output, then a 2-feet coaxial cable toward a T-plug. One side is for the LeCroy scope (with its probe), and the other for the DSO (with its probe).

Nothing else.

Hereinafter I will not mention what on the reference scope I see, because I have checked that is always as on the generator has been set. On the reference scope the square wave has a 20ns rise time, as well a 20ns falling time. This is constant over the various test below. The shape of the square wave is almost perfect, at a glance.

The waves outputted from the generator are perfectly balanced on zero Volts, that is a 1 Vpp sine looks like a Sin(t) function, having an amplitude of 500 mV.

On the DSO is always use only the channel A, the others are disconnected (without any probe). The channel B is hidden, but trying to enable it I didn’t notice any significative modification of the A track.

Over the tests, I have kept the DSO with DC coupling; also switching to AC no noticeable change of behavior/shape.

The triggering I have tested is NORM or AUTO, always using a rising (i.e. positive) slope.

I have also noticed that the amplitude measured with DSO is slightly less than the real one: it shows about 90% of the reference scope. That for low frequencies, so there is not any bandwidth limitation.

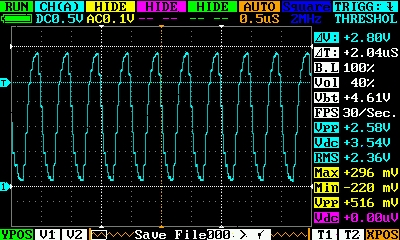

Test #1: 100KHz square wave @ 1Vpp

The DSO shows a well-shaped square and pretty stable. With NORM triggering it seems working well, although you have to serach carefully the stability level. That is strange because the wave is tall enough to find the voltage step. It seems there is no problem even switching the timebase to 100ns/div.

By using the AUTO triggering, the things are gettings worser: from 1us/div and above it seems working okay, but under 1us/div the wave is getting crazy: unstable and heavily deformed, not recognizable as a square. It looks much more a digital message, instead of a perfect wave. However, by adjusting the triggering level you may find a stability point. What the level does in AUTO mode?

When the square wave is stable, at 100ns/div, the rising/falling step of the wave is measurable: let’s say around 200ns, maybe slightly less.

Test #2: 500KHz square wave @ 1Vpp

Same as above. The wave displayed begins to be “rounded”, because of the rising/falling time. However not a bad shape.

Test #3: 1MHz square wave @ 1Vpp

Same as above.

Test #4: 2MHz square wave @ 1Vpp

Same as above.

Test #5: 3.5MHz square wave @ 1Vpp

Same as above. The wave period is shorter than the rising+falling time and the wave looks much more a sine than a square. The trigger ability to catch the signal seems begin faulting: it is always more hard to find the right point to keep the wave stable.

Test #6: 100KHz sine wave @ 1Vpp

The sine looks perfect.

Test #7: 1MHz sine wave @ 1Vpp

The sine still looks perfect.

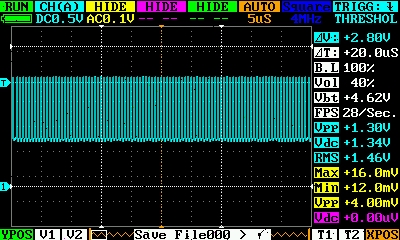

Test #8: 5MHz sine wave @ 1Vpp

The sine still looks like a sine, but its aplitude is about 700mVpp. No matter what t/div you choose. It is also valid all the considerations for the trigger modes and their instability, as seen for the square wave.

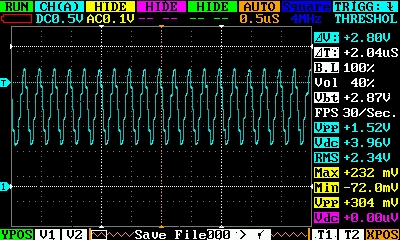

Test #9: 10MHz sine wave @ 1Vpp

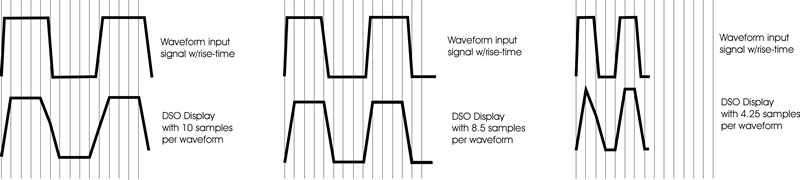

The sine is step-shaped, but it is absolutely normal because of the sampling. At 100ns/div you may easiliy count 7 steps for each sine period. Every step is really well shaped, that is the track-and-hold section is performing its task very well.

The amplitude of the wave is almost 400mVpp, that is less than an half of the real input. The funniest thing is that the DSO is set at 200mV/div, but it seems that is not possibile to magnify. By trying to set 100mV/div or less, the wave (i.e. the scope) don’t care at all. There is not any perceivable magnification. This strange bahavior is firing me a suspect: will the actual amplitude read by the ADC about 400mVpp or less? Ya, because if I switch to 50mV/div, the wave displayed is still about 2 divs…so it is almost 400mV or almost 100mV???

Test #10: elevating the generator amplitude

It seems there is no significative way to get better performance, even by feeding a 5Vpp signal on input.

That’s all.

I hope that clarify some doubt about the analog section of the DSO.

The length of these posts demonstrates the complexity of these discussions.

The length of these posts demonstrates the complexity of these discussions.

.

.